### FEATURES

- R<sub>SENSE</sub>: 50mΩ ± 0.5%

- Fully Assembled and Tested

- > 2in x 2in 2-layer circuit board

# **COMPONENT LIST**

| DESIGNATION | QTY | DESCRIPTION      |

|-------------|-----|------------------|

| C2          | 1   | 47nF ±10%        |

|             |     | capacitor (0805) |

| R1          | 1   | 50mΩ ± 0.5%      |

|             |     | (0805)           |

| U1          | 1   | TS1103-25DB/     |

|             |     | TS1103-50DB/     |

|             |     | TS1103-100DB/    |

|             |     | TS1103-200DB     |

| VDD, VBATT, | 5   | Test points      |

| VOUT, SIGN, |     |                  |

| LOAD        |     |                  |

#### DESCRIPTION

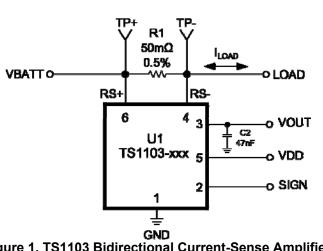

The demo board for the TS1103 is a completely assembled and tested circuit board that can be used for evaluating the bidirectional current-sense amplifier for all (4) gain options; i.e., 25V/V, 50V/V, 100V/V, and 200V/V.

The board is configured with an  $R_{SENSE} = R1=50m\Omega$  resistor. The board has a dedicated RS+=VBATT, RS-=LOAD, output voltage OUT=VOUT, VDD, and SIGN test points. For additional information, refer to the TS1103 product datasheet.

All TS1103s are available in a PCB-space saving 6-lead SOT23 surface-mount package.

Product data sheets and additional documentation can be found on the factory web site at <u>www.touchstonesemi.com</u>.

## **ORDERING INFORMATION**

| Order Number | Description |

|--------------|-------------|

| TS1103-25DB  |             |

| TS1103-50DB  | TS1103-XXX  |

| TS1103-100DB | Demo Board  |

| TS1103-200DB |             |

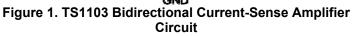

Figure 2. TS1103 Demo Board

#### DESCRIPTION

The TS1103 demo board includes decoupling capacitor pads, C1, at the VBATT input pin and a 47nF capacitor at the VOUT output pin. Because the TS1103 is a bidirectional current-sense amplifier, the demo board can be set-up to sense current in both directions. Please refer to Table 2 for the proper connections of VBATT and LOAD test points. The direction of the current is known based on the voltage level of the SIGN pin. If  $V_{RS+}$ > $V_{RS-}$ , the SIGN pin is a logic HIGH or VDD voltage. If  $V_{RS-}$ > $V_{RS+}$ , the SIGN pin is a logic LOW or GND voltage. A VDD test point is available and powers the internal comparator that monitors the direction of the comparator is the voltage on the SIGN pin.

## QUICK START PROCEDURE

#### **Required Equipment**

- A TS1103 demo board

- A dual output, DC power supply, an HP Model HP6624A or equivalent

- > Three digital voltmeters

- A load resistor or an active load (value varies depending on I<sub>LOAD</sub> desired)

| Signal | Demo board |  |  |

|--------|------------|--|--|

| RS+    | VBATT      |  |  |

| RS-    | LOAD       |  |  |

| OUT    | VOUT       |  |  |

| GND    | GND        |  |  |

| VDD    | VDD        |  |  |

| SIGN   | SIGN       |  |  |

| -      |            |  |  |

Table 1. Demo Board Test Points

| Test Point | V <sub>RS+</sub> >V <sub>RS-</sub> | V <sub>RS-</sub> >V <sub>RS+</sub> |  |

|------------|------------------------------------|------------------------------------|--|

| VBATT      | input voltage                      | load                               |  |

| LOAD       | load                               | input voltage                      |  |

Table 2. VBATT and LOAD Test Point Connections Per ILOAD Direction

| GAIN<br>(V/V) | V <sub>BATT</sub><br>(V) | I <sub>LOAD</sub><br>(mA) | V <sub>DD</sub><br>(V) | R <sub>LOAD</sub><br>(Ω) | V <sub>OUT</sub><br>(V) | MAX<br>V <sub>SENSE</sub><br>(mV) |

|---------------|--------------------------|---------------------------|------------------------|--------------------------|-------------------------|-----------------------------------|

| 25            | 6                        | 1600                      | 1.8                    | 3.75                     | 2                       | 80                                |

| 50            | 6                        | 800                       | 1.8                    | 7.5                      | 2                       | 40                                |

| 100           | 6                        | 400                       | 1.8                    | 15                       | 2                       | 20                                |

| 200           | 6                        | 200                       | 1.8                    | 30                       | 2                       | 10                                |

Table 3. Demo Board Test Set-Up Per Gain Setting

To evaluate the TS1103 bidirectional current-sense amplifier circuit, the following steps are to be performed:

- Before connecting the DC power supply to the demo board, turn on the power supply, set the DC voltage to 6V on one output and the other to 1.8V. Set the short circuit current limit on each output to 10% higher than the maximum load current in the application, and then turn it off.

- 2) For applications where  $V_{RS+}>V_{RS-}$ , connect the 6V DC power supply positive terminal to the test point VBATT and its negative terminal to the test point GND. Connect the 1.8V power supply positive terminal to the test point VDD and its negative terminal to the test point GND. See Table 2 for applications where  $V_{RS-}>V_{RS+}$ .

- 3) Connect a digital voltmeter to the test points TP+ and TP- to measure  $V_{\mbox{\scriptsize SENSE}}.$

- 4) Connect the positive terminal of a second digital voltmeter to the test point VOUT and the negative terminal to the test point GND.

- 5) To monitor the direction of the current, connect the positive terminal of a third digital voltmeter to the test point SIGN and the negative terminal to the test point GND.

- 6) Based on the selected gain option of the current sense amplifier, select the load resistor or an active load according to Table 3. Connect one end of this resistor or active load to the test point LOAD and the other end to the test point GND.

- Turn on the power supply and observe the output voltage at VOUT. The expression for the TS1103's output voltage is given by:

$$VOUT = I_{LOAD} \times 50 m\Omega \times \frac{ROUT}{RGAIN[A/B]}$$

where the TS1103's internal ROUT and RGAIN[A/B] resistor values are listed in Table 4.

| GAIN(V/V) | RGAIN[A/B] (Ω) | ROUT (Ω) |  |

|-----------|----------------|----------|--|

| 25        | 400            | 10k      |  |

| 50        | 200            | 10k      |  |

| 100       | 100            | 10k      |  |

| 200       | 100            | 20k      |  |

Table 4. TS1103's Internal Gain Setting Resistors (typical values)

The TS1103's actual output voltage VOUT will depend on the TS1103's actual offset voltage V<sub>OS</sub>, its gain error GE, sense resistor (R<sub>SENSE</sub>) tolerance of ±1%, and the load resistor tolerance/active load accuracy.

**Note:** For applications where  $V_{RS-}$  > $V_{RS+}$ , connect test points VBATT and LOAD based on Table 2 and follow the steps above.

Figure 3. Top Layer Component View

Figure 4. Top Layer Trace View